# Radiation Effects in MOS Oxides

James R. Schwank, *Fellow, IEEE*, Marty R. Shaneyfelt, *Fellow, IEEE*, Daniel M. Fleetwood, *Fellow, IEEE*, James A. Felix, *Member, IEEE*, Paul E. Dodd, *Senior Member, IEEE*, Philippe Paillet, *Senior Member, IEEE*, and Véronique Ferlet-Cavrois, *Senior Member, IEEE*

**Abstract**—Electronic devices in space environments can contain numerous types of oxides and insulators. Ionizing radiation can induce significant charge buildup in these oxides and insulators leading to device degradation and failure. Electrons and protons in space can lead to radiation-induced total-dose effects. The two primary types of radiation-induced charge are oxide-trapped charge and interface-trap charge. These charges can cause large radiation-induced threshold voltage shifts and increases in leakage currents. Two alternate dielectrics that have been investigated for replacing silicon dioxide are hafnium oxides and reoxidized nitrided oxides (RNO). For advanced technologies, which may employ alternate dielectrics, radiation-induced voltage shifts in these insulators may be negligible. Radiation-induced charge buildup in parasitic field oxides and in SOI buried oxides can also lead to device degradation and failure. Indeed, for advanced commercial technologies, the total-dose hardness of ICs is normally dominated by radiation-induced charge buildup in either parasitic field oxides and/or SOI buried oxides. Heavy ions in space can also degrade the oxides in electronic devices through several different mechanisms including single-event gate rupture, reduction in device lifetime, and large voltage shifts in power MOSFETs.

**Index Terms**—Aging, MOS devices, oxide breakdown, power MOSFETs, radiation effects, silicon-on-insulator, total dose effects.

## I. INTRODUCTION

FROM MOSFETs to bipolar ICs, oxides and insulators are key components of many electronic devices. Ionizing radiation can induce significant charge buildup in these oxides and insulators leading to device degradation and failure. In space systems (and other harsh radiation environments, e.g., high-energy particle accelerators), exposure to high fluxes of electrons and protons can significantly reduce system lifetime due to total ionizing dose. Over the last thirty years, the effects of total ionizing dose on radiation-induced charge buildup in oxides have been investigated in detail. In addition to total ionizing dose effects, the energetic particles of space can also induce degradation by other mechanisms. For example, the heavy ions in space

Manuscript received November 6, 2007; revised May 16, 2008. Current version published September 19, 2008. This work was supported by the Defense Threat Reduction Agency under DTRA IACRO 07-4196I and the U. S. Department of Energy. Sandia is a multiprogram laboratory operated by Sandia Corporation, a Lockheed Martin Company, for the U.S. Department of Energy's National Nuclear Security Administration under Contract DE-AC04-94AL85000.

J. R. Schwank, M. R. Shaneyfelt, J. A. Felix, and P. E. Dodd are with Sandia National Laboratories, Albuquerque, NM 87185 USA (e-mail: schwanjr@sandia.gov).

D. M. Fleetwood is with Vanderbilt University, Nashville, TN 37235 USA.

P. Paillet and V. Ferlet-Cavrois are with CEA-DIF, 91680 Bruyères-le-Châtel, France.

Color versions of one or more of the figures in this paper are available online at <http://ieeexplore.ieee.org>.

Digital Object Identifier 10.1109/TNS.2008.2001040

environments can reduce long-term reliability and lead to catastrophic device failure.

In this paper, we review the effects of radiation on oxide-induced device degradation and failure. The effects of total ionizing dose radiation-induced charge buildup in  $\text{SiO}_2$  and alternative high-k gate dielectrics, field isolation, and silicon-on-insulator (SOI) buried oxides, and oxide hardening techniques are first reviewed. The effects of aging and pre-irradiation elevated temperature stress on MOS and bipolar radiation response are also discussed. After that, the mechanisms and properties of heavy ion-induced single-event gate rupture (SEGR) will be discussed, followed by a brief discussion of the effects of heavy-ion exposure on long-term reliability.

## II. TOTAL-DOSE EFFECTS

### A. Overview

High-energy electrons (secondary electrons generated by photon interactions or electrons present in the environment) and protons can ionize atoms, generating electron-hole pairs. As long as the energies of the electrons and holes generated are higher than the minimum energy required to create an electron-hole pair, they can in turn generate additional electron-hole pairs. In this manner, a single, high-energy incident photon, electron, or proton can create thousands of electron-hole pairs.

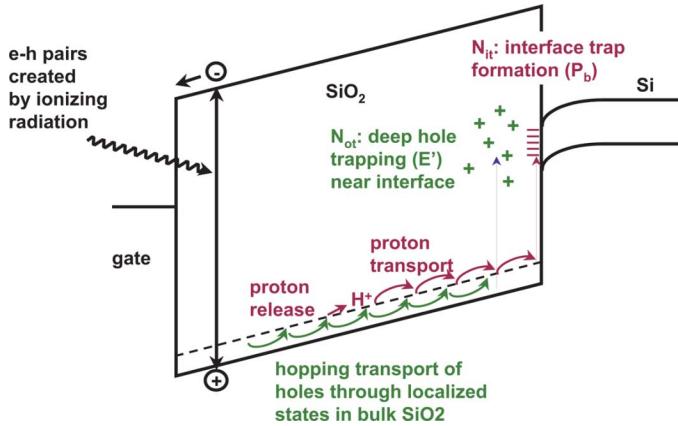

When an MOS transistor is exposed to high-energy ionizing irradiation, electron-hole pairs are created in the oxide. Electron-hole pair generation in the oxide leads to almost all total dose effects. The generated carriers induce the buildup of charge, which can lead to device degradation. The mechanisms by which device degradation occurs are depicted in Fig. 1. Fig. 1 is a plot of an MOS band diagram for a p-substrate capacitor with a positive applied gate bias. Immediately after electron-hole pairs are created, most of the electrons will rapidly drift (within picoseconds) toward the gate and holes will drift toward the  $\text{Si}/\text{SiO}_2$  interface. However, even before the electrons leave the oxide, some of the electrons will recombine with holes. The fraction of electron-hole pairs that escape recombination is called the electron-hole yield or charge yield. Those holes which escape “initial” recombination will transport through the oxide toward the  $\text{Si}/\text{SiO}_2$  interface by hopping through localized states in the oxide. As the holes approach the interface, some fraction will be trapped, forming a positive oxide-trap charge. It is believed that hydrogen ions (protons) are likely released as holes “hop” through the oxide or as they are trapped near the  $\text{Si}/\text{SiO}_2$  interface. The hydrogen ions can also drift to the  $\text{Si}/\text{SiO}_2$  where they may react to form interface traps. At threshold, interface traps are predominantly positively

Fig. 1. Band diagram of an MOS capacitor with a positive gate bias. Illustrated are the main processes for radiation-induced charge generation.

charged for p-channel transistors and negatively charged for n-channel transistors.

In addition to oxide-trapped charge and interface-trap charge buildup in gate oxides, charge buildup will also occur in other oxides including field oxides, silicon-on-insulator (SOI) buried oxides, and alternate dielectrics. The radiation-induced charge buildup in these insulators can cause device degradation and circuit failure. Positive charge trapping in the gate oxide can invert the channel interface causing leakage current to flow in the OFF state condition ( $V_{GS} = 0$  V). This will result in an increase in the static power supply current of an IC and may also cause IC failure. In a similar fashion, positive charge buildup in field and SOI buried oxides can cause large increases in IC static power supply leakage current (caused by parasitic leakage paths in the transistor). In fact, for advanced ICs with very thin gate oxides, radiation-induced charge buildup in field oxides and SOI buried oxides normally dominates the radiation-induced degradation of ICs. Large concentrations of interface-trap charge can decrease the mobility of carriers and increase the threshold voltage of n-channel MOS transistors. These effects will tend to decrease the drive of transistors, degrading timing parameters of an IC. In the rest of this section, we present the details of oxide-trap and interface-trap charge buildup in MOS transistors.

### B. Charge Yield

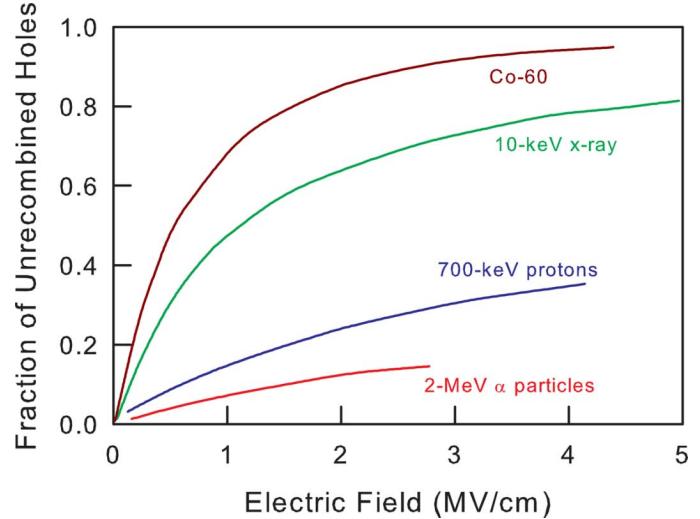

If an electric field exists across the oxide of an MOS transistor, once generated, electrons in the conduction band and holes in the valence band will immediately begin to transport in opposite directions. Electrons are extremely mobile in silicon dioxide and are normally swept out of silicon dioxide in picoseconds [1], [2]. However, even before the electrons can leave the oxide, some fraction of the electrons will recombine with holes in the oxide valence band. This is referred to as initial recombination. The amount of initial recombination is highly dependent on the electric field in the oxide and the energy and type of incident particle [3]. In general, strongly ionizing particles form dense columns of charge where the recombination rate is relatively high. On the other hand, weakly ionizing particles generate relatively isolated charge pairs, and the recombination rate is lower [3]. The dependence of initial recombination on the electric field strength in the oxide for low-energy protons,

Fig. 2. The fraction of holes that escape initial recombination (charge yield) for x rays, low-energy protons, gamma rays, and alpha particles. (After [4] and [5].)

alpha particles, gamma rays (Co-60), and x rays is illustrated in Fig. 2 [4], [5]. Plotted in Fig. 2 is the fraction of unrec combined holes (charge yield) versus electric field in the oxide. The data for the Co-60 and 10-keV x-ray curves were taken from [5]. The other two curves were taken from [4]. For all particles, as the electric field strength increases, the probability that a hole will recombine with an electron decreases, and the fraction of unrec combined holes increases. Taking into account the effects of hole yield and electron-hole pair generation, the total number of holes generated in the oxide (not including dose enhancement effects [3], [4] that escape initial recombination,  $N_h$ , is given by [4]

$$N_h = f(E_{ox})g_0 D t_{ox} \quad (1)$$

where  $f(E_{ox})$  is the hole yield as a function of oxide electric field,  $D$  is the dose, and  $t_{ox}$  is the oxide thickness (in units of cm).  $g_0$  is a material-dependent parameter giving the initial charge pair density per rad of dose ( $g_0 = 8.1 \times 10^{12}$  pairs/cm<sup>3</sup> per rad for SiO<sub>2</sub> [4]).

### C. Oxide Traps

Holes generated in the oxide transport much slower through the lattice than electrons [1]. In the presence of an electric field, holes can transport to either the gate/SiO<sub>2</sub> (negatively applied gate bias) or the Si/SiO<sub>2</sub> interface (positively applied gate bias). Due to its charge, as a hole moves through the SiO<sub>2</sub> it causes a distortion of the local potential field of the SiO<sub>2</sub> lattice. This local distortion increases the trap depth at the localized site, which tends to confine the hole to its immediate vicinity. Thus, in effect, the hole tends to trap itself at the localized site. The combination of the charged carrier (hole) and its strain field is known as a polaron [6]. As a hole transports through the lattice, the distortion follows the hole. Hence, holes transport through SiO<sub>2</sub> by "polaron hopping" [4], [7], [8]. Polarons increase the effective mass of the holes and decrease their mobility. Polaron

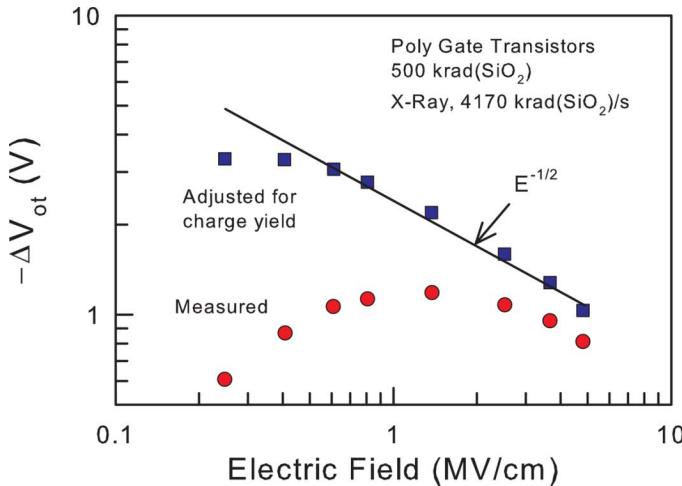

Fig. 3. Electric field dependence of  $\Delta V_{ot}$  versus electric field. Shown are the measured data (circles) and the measured data corrected for charge yield (squares). (After [10].)

hopping makes hole transport dispersive (i.e., hole transport occurs over many decades in time after a radiation pulse) and very temperature and oxide thickness dependent [4], [7], [8].

With the application of a positive gate bias, holes transport to the Si/SiO<sub>2</sub> interface. Close to the interface there are a large number of oxygen vacancies due to the out-diffusion of oxygen in the oxide [9] and lattice mismatch at the surface. These oxygen vacancies can act as trapping centers. As holes approach the interface, some fraction of the holes will become trapped. The number of holes that are trapped is given by the capture cross-section near the interface, which is dependent on the applied field and is very device fabrication dependent, with only a few percent of the holes being trapped in hardened oxides to as much as 50 to 100% for soft oxides. The positive charge associated with trapped holes causes a negative threshold-voltage shift in both n- and p-channel MOS transistors.

The effect of the capture cross-section on trapped-hole buildup can be observed in the electric field dependence of the buildup of oxide traps shortly after irradiation. Fig. 3 is a plot of the threshold-voltage shift due to oxide-trap charge,  $\Delta V_{ot}$ , versus oxide electric field [10]. The circles are the measured data, the squares are the measured data adjusted for charge yield, and the solid line is a plot of  $E^{-1/2}$ . For electric fields greater than 0.5 V/cm,  $\Delta V_{ot}$  adjusted for charge yield decreases with approximately an  $E^{-1/2}$  electric field dependence. This is the same electric field dependence as is observed for the hole capture cross-section near the Si/SiO<sub>2</sub> interface [3], [11]–[15]. This indicates that the field dependence of oxide-trap charge buildup is determined primarily by the hole capture cross-section.

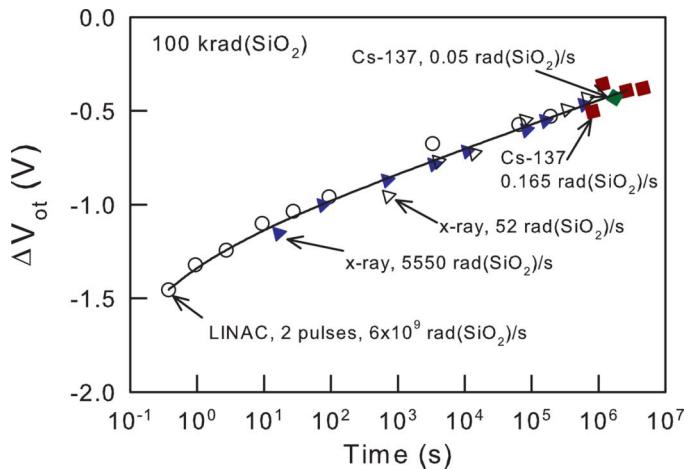

Immediately after charge is trapped in oxides it begins to be neutralized. The time dependence of trapped-hole neutralization at room temperature is illustrated in Fig. 4 [16], where the voltage shift due to oxide-trap charge,  $\Delta V_{ot}$ , is plotted versus time for hardened n-channel polysilicon gate transistors irradiated to 100 krad(SiO<sub>2</sub>) at dose rates from  $6 \times 10^9$  to 0.05 rad(SiO<sub>2</sub>)/s and then annealed under bias at room temperature. The bias during irradiation and anneal was 6 V and

Fig. 4. Oxide-trapped charge neutralization during anneal at room temperature for transistors irradiated at dose rates from  $6 \times 10^9$  to 0.05 rad(SiO<sub>2</sub>)/s. (After [16].)

the gate oxide thickness of the transistors was 60 nm. During anneal, the decrease in the magnitude of  $\Delta V_{ot}$  follows a logarithmic time dependence. At each dose rate,  $\Delta V_{ot}$  falls on the same straight line. These data show that  $\Delta V_{ot}$  increases with dose rate if  $\Delta V_{ot}$  is measured immediately after irradiation. However, as long as the total time of irradiation and anneal is the same,  $\Delta V_{ot}$  dose not depend on the dose rate of the radiation source. The actual rate at which  $\Delta V_{ot}$  is neutralized can depend on the details of the device fabrication process [17].

The neutralization of oxide-trapped charge occurs primarily by one of two mechanisms: 1) the tunneling of electrons from the silicon into either oxide traps [17]–[22] or electron traps associated with trapped holes [23], and/or 2) the thermal emission of electrons from the oxide valence band into oxide traps [18], [22], [24]–[26]. Electron tunneling into electron traps associated with trapped holes results in a charge neutral state, but does not remove the trapped hole. The spatial and energy distributions of the oxide traps will strongly affect the rate at which charge neutralization occurs. For tunneling, the spatial distribution of the oxide traps must be close to the Si/SiO<sub>2</sub> interface. For thermal emission, the energy levels of the oxide traps must be close to the oxide valence band. Not only will the spatial and energy distributions of the oxide traps affect the rate of neutralization at room temperature and constant bias, but they will also affect its temperature and bias dependence. By reversing the polarity of the bias, electrons can tunnel back into the silicon substrate and some fraction of the original amount of oxide-trapped charge can be restored.

#### D. Interface Traps

In addition to oxide traps, radiation also leads to the formation of interface traps at the Si/SiO<sub>2</sub> interface [27]. Interface traps exist within the silicon band gap at the interface. Because of their location at the interface and energy levels within the Si band gap, the charge of an interface trap can be changed easily by applying an external bias.

Interface traps can be positive, neutral, or negative. Traps in the lower portion of the band gap are predominantly donors; i.e., if the Fermi level at the interface is below the trap energy level,

Fig. 5. Interface-trap buildup as a function of time after irradiation. (After [33].)

the trap “donates” an electron to the silicon. In this case, the trap is positively charged. P-channel transistors at threshold are affected primarily by interface traps in the lower region of the band gap. Therefore, for a p-channel transistor, interface traps are predominantly positive, causing negative threshold-voltage shifts. Conversely, traps in the upper portion of the band gap are predominantly acceptors; i.e., if the Fermi level is above the trap energy level, the trap “accepts” an electron from the silicon. In this case, the trap is negatively charged. Interface traps predominantly in the upper region of the band gap affect an n-channel transistor at threshold. Therefore, for an n-channel transistor, interface traps are predominantly negative, causing positive threshold-voltage shifts. At midgap, interface-trap charge is approximately neutral [28]–[31]. Because oxide-trap charge is positive for both p- and n-channel transistors, oxide-trap charge and interface-trap charge compensate each other for n-channel transistors and add together for p-channel transistors.

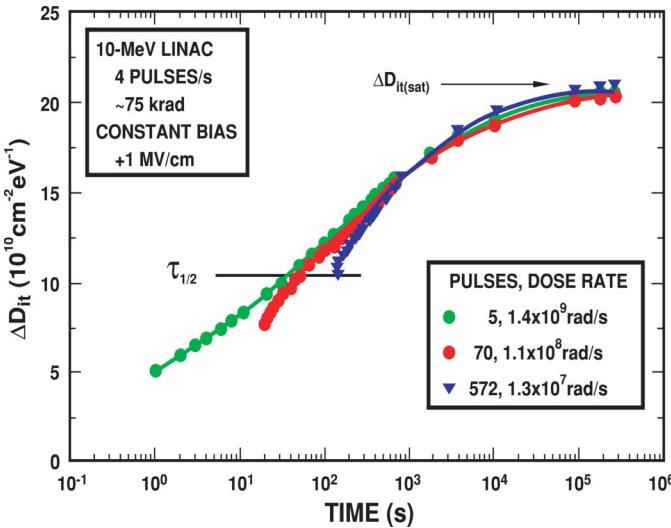

Interface-trap buildup occurs on time frames much slower than oxide-trap charge buildup. Interface-trap buildup can take thousands of seconds to saturate after a pulse of ionizing radiation [32], [33]. Fig. 5 [33] is a plot of the increase in density of interface-traps,  $\Delta D_{it}$ , versus time after high-dose-rate pulses of ionizing radiation. The density of interface traps is the average number of traps in a given interval of the band gap, and has the units of traps/cm<sup>2</sup>-eV. The data for this plot were taken on polysilicon gate transistors irradiated to 75 krad(Si) in 5, 70, and 572 pulses at a 4-Hz repetition rate using an electron linear accelerator (LINAC). The gate oxide thickness was 47 nm and the electric field across the oxide during irradiation and anneal was 1 MV/cm. For these measurements, interface-trap buildup had begun by the time of the first measurement (1 s for the data taken with 5 pulses). However, interface-trap buildup does not begin to saturate until  $\sim 10^5$  s. This curve is typical of that for interface-trap buildup. For the curve taken with 5 pulses, the time for 50% buildup ( $\tau_{1/2}$ ) is approximately 35 s.

For polysilicon-gate transistors, the electric field dependence of interface-trap buildup is very similar to the electric field

Fig. 6. Interface-trap buildup for transistors irradiated at dose rates from  $6 \times 10^9$  to  $0.05$  rad(SiO<sub>2</sub>)/s and annealed under bias (+6 V) at room temperature. (After [16].)

dependence of oxide-trap charge buildup [10], [34]. When measured data are adjusted for charge yield, the adjusted data follow an  $E^{-0.6}$  field dependence, within experimental uncertainty equal to the electric field dependence of oxide-trap charge and the hole capture cross-section near the interface. This is an indication that both oxide-trap charge and interface-trap charge buildup are linked to hole trapping near the Si/SiO<sub>2</sub> interface. Little or insignificant buildup of interface traps occurs if a negative bias is maintained during irradiation and anneal, consistent with the lack of hole trapping near the interface under these conditions.

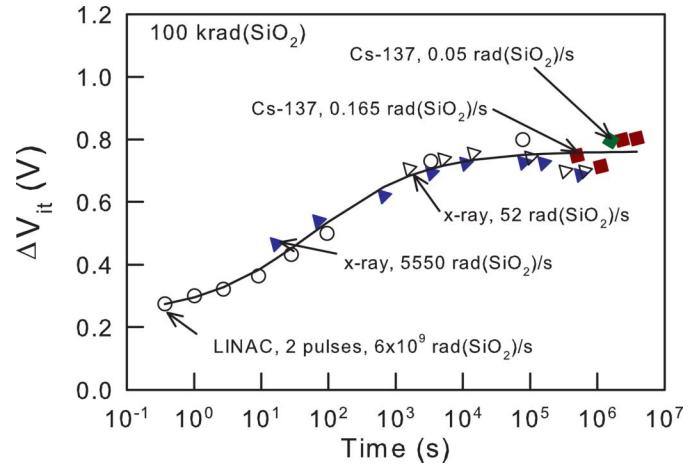

Although some workers have suggested that there can be a dose rate dependence for interface-trap buildup [35], in general, there does not appear to be a “true” dose-rate dependence for the buildup of interface traps in MOS devices [16]. Fig. 6 [16] is a plot of  $\Delta V_{it}$  versus time for transistors irradiated to a total dose of 100 krad(SiO<sub>2</sub>) at dose rates from  $6 \times 10^9$  to  $0.05$  rad(SiO<sub>2</sub>)/s. After irradiation each transistor was annealed under bias. The bias during irradiation and anneal was 6 V. Note that, as long as the total irradiation plus anneal time is the same, the same threshold-voltage shift due to interface traps is measured, regardless of the dose rate of the radiation source. If there were a “true” dose-rate dependence, the data taken at different dose rates would not fall on the same response curve.

Unlike oxide-trap charge, interface traps do not readily anneal at room temperature. Some interface-trap annealing at 100°C has been reported by several workers [36]–[39]. Other workers have suggested that some interface-trap annealing could also occur at temperatures below 100°C for MOS [39] and bipolar [40] devices. However, higher temperatures are normally required to observe significant interface-trap annealing [41], [42]. These properties make interface-trap charge effects very important for low dose-rate applications, e.g., space. For n and p-channel MOS transistors, interface traps affect device performance primarily through an increase in threshold voltage and a decrease in channel mobility. Both of these degradation mechanisms tend to reduce the drive current of “ON” transistors, leading to increases in timing parameters of an IC.

### E. Device Properties

For a gate oxide transistor, parasitic field oxide transistor, or back-channel transistor of an SOI device (discussed below), the total threshold-voltage shift is the sum of the threshold-voltage shifts due to oxide-trap and interface-trap charge, i.e.,

$$\Delta V_{th} = \Delta V_{ot} + \Delta V_{it}. \quad (2)$$

$\Delta V_{ot}$  and  $\Delta V_{it}$  can be determined from

$$\Delta V_{ot, it} = \frac{-1}{C_{ox} t_{ox}} \int_0^{t_{ox}} \rho_{ot, it}(x) x dx \quad (3)$$

where  $\rho_{ot, it}(x)$  is the charge distribution of radiation-induced oxide-trapped or interface-trap charge. Note the change in sign between the charge distribution and the threshold-voltage shift. For positive charge, the threshold-voltage shift is negative; conversely, for a negative charge, the threshold-voltage shift is positive. Thus, for devices where oxide-trap charge dominates, the threshold-voltage shift will be predominantly negative.

At high dose rates and short times, little neutralization of oxide-trap charge will occur and  $\Delta V_{ot}$  can be large and negative. Conversely, interface-trap charge will have had insufficient time to build up and  $\Delta V_{it}$  is normally small. Thus, at high dose rates and short times for either n- or p-channel transistors, the threshold-voltage shift can be large and negative. For an n-channel transistor (gate or parasitic field oxide transistor), large negative threshold-voltage shifts can significantly increase the drain-to-source leakage current, which in turn causes significant increases in IC static supply leakage current,  $I_{DD}$ , leading to potential IC failure.

At moderate dose rates, some neutralization of oxide-trap charge will take place and some buildup of interface traps will also occur. Thus, for this case, both  $\Delta V_{ot}$  and  $\Delta V_{it}$  can be large. For an n-channel transistor,  $\Delta V_{ot}$  and  $\Delta V_{it}$  tend to compensate each other. Therefore, at moderate dose rates, even though the individual components ( $\Delta V_{ot}$  and  $\Delta V_{it}$ ) of the threshold-voltage shift can be large, the net threshold-voltage shift for an n-channel transistor can be small and the radiation-induced failure level of an IC may be relatively high.

For the long times associated with low-dose-rate irradiations, a large fraction of the oxide-trap charge in transistors may be neutralized during irradiation. Thus,  $\Delta V_{ot}$  is often small. In contrast, the long times associated with low-dose-rate irradiations allow interface-trap buildup to saturate. This results in a positive increase in threshold voltage in n channel transistors and a decrease in carrier mobility. The buildup of interface traps in gate oxides is primarily important for older technologies and other device types (e.g., power MOSFETs) with relatively thick oxides. For present-day gate oxides, the gate oxide thickness is normally very thin. As will be shown below, radiation-induced charge buildup rapidly decreases with decreasing oxide thickness. As a result, interface-trap buildup (and oxide-trapped charge buildup) in gate oxides is often not a concern and total dose effects are dominated by oxide-trapped charge buildup in field oxides, even at low dose rates.

For p-channel transistors, both  $\Delta V_{ot}$  and  $\Delta V_{it}$  are negative and they add together. At high dose rates,  $\Delta V_{ot}$  can be large. At low dose rates,  $\Delta V_{ot}$  can still be large because standard bias conditions for a p-channel transistor do not lead to significant oxide-trap charge neutralization via tunneling. In addition,  $\Delta V_{it}$  can also be large, especially for thick oxides (e.g., parasitic field oxides). Therefore, for both high and low dose rates, the threshold-voltage shift for p-channel transistors can be large and negative. The net result is that for parasitic p-channel field oxide transistors, the threshold becomes larger, decreasing the effect of radiation-induced charge buildup in parasitic field oxides (over p-type regions) on radiation-induced degradation.

In most works comparing the radiation-induced degradation of MOS devices at laboratory and space environments, MOS device response at low dose rates can be estimated by irradiating devices at laboratory dose rates and annealing devices postirradiation under bias [43], [44]. This is because the mechanisms for MOS device degradation at laboratory and low dose rates are normally the same. This is unlike enhanced low dose rate sensitivity (ELDRS) that is often observed in bipolar devices [45] where the amount of radiation-induced degradation can be significantly more at low dose rates than at laboratory dose rates even after a long-term anneal of the laboratory dose rate irradiated devices. Recent work has shown that ELDRS effects can also be observed in MOS devices [46]. In this work, the edge leakage current due to radiation-induced charge buildup in field oxides of nMOS transistors was more at low dose rates than at laboratory dose rates followed by an equivalent long-term anneal. The enhanced degradation at low dose rates was attributed to space charge in the field oxides altering the the spatial distribution of trapped holes and lowering the annealing rate at low dose rates.

### F. Radiation-Induced Leakage Current

A phenomenon that has been associated specifically with ultra-thin gate oxides is radiation-induced leakage current (RILC) [47]. RILC is an increase in leakage current that is observed at low-electric fields and occurs after exposing an ultra-thin gate oxide to relatively high total doses of ionizing radiation. It is a potential device reliability concern and is similar to stress-induced leakage current (SILC) that occurs after stressing an oxide with a high electric field.

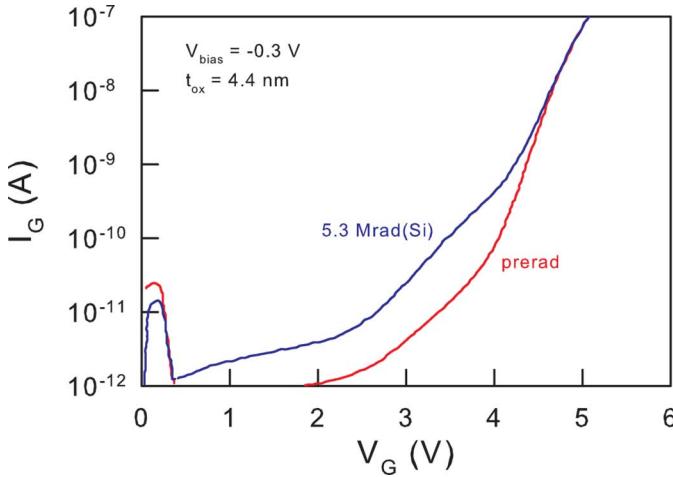

RILC was first observed by Scarpa, *et al.* in 1997 and is illustrated in Fig. 7. This figure is a plot of the gate leakage current,  $I_G$ , versus gate voltage,  $V_G$ , for a non-irradiated p-substrate capacitor and a capacitor irradiated to 5.3 Mrad(Si) with Co-60 gamma rays at a gate bias of 0.3 V. The oxide thickness was 4.4 nm. The I-V curves were taken by sweeping the gate bias from zero to positive values. At low gate biases (electric fields),  $I_G$  is larger for the irradiated capacitor than for the non-irradiated capacitor. For the irradiation bias used, the electric field across the oxide is well below that required to observe SILC. This suggests that the larger values of  $I_G$  for the irradiated capacitor are indeed radiation induced. The fact that the high-field characteristics of the non-irradiated and the irradiated capacitors are similar suggests that the amount of radiation-induced oxide-trapped charge is negligible [48]. RILC increases with decreasing oxide thickness and increasing total dose [48]. The

Fig. 7. Gate-oxide leakage current versus gate voltage for a non-irradiated capacitor and a capacitor irradiated to 5.3 Mrad(Si) with Co-60 gamma rays with a gate bias of  $-0.3$  V. The larger leakage current values at low electric fields for the irradiated capacitor illustrates radiation-induced leakage current (RILC). (After [47].)

increase in RILC with total dose is approximately linear. This implies that the neutral oxide defect density increases approximately linearly with dose.

RILC has been observed for a wide range of radiation sources and particles including Co-60 gamma rays [47], 8-MeV electrons [48], [49] from a linear accelerator, 10-keV x rays, and heavy ions [49]. The mechanism for RILC has been attributed to be an inelastic tunneling process assisted by neutral traps in the oxide [47], [48]. During exposure to ionizing irradiation, neutral electron traps are created in the bulk of the oxide. With a positively applied bias to the gate, electrons in the silicon conduction band can tunnel first into the neutral electron trap and then into the gate. Because electron tunneling causes RILC, RILC will have a strong oxide thickness dependence, with RILC increasing with decreasing oxide thickness. This model is supported by solutions of the quantum-mechanical Schrödinger equation for the probability of an electron tunneling through the oxide [50]. Experimental agreement between model simulations and experimental data has been obtained using a double gaussian distribution in space and in energy for the neutral electron trap. It is likely that the neutral electron trap originates as radiation-induced holes are trapped at E' centers in the oxide [48], [51]. (Most E' centers are characterized by an unpaired electron highly localized on a silicon atom bonded to three oxygen atoms.) Electron paramagnetic resonance measurements have shown a link between E' centers and RILC [51]. The neutral trap distribution is influenced by the electric field during irradiation, making RILC bias dependent. For nitrided ultra-thin oxides, the peak in RILC was found to occur near zero oxide electric field.

### III. OXIDE HARDENING

In this section, we examine process conditions that affect oxide hardness. Although we will focus on process conditions that affect gate oxide hardness, the process conditions discussed have similar effects on radiation-induced charge buildup in field isolation insulators and silicon-on-insulator buried oxides. A

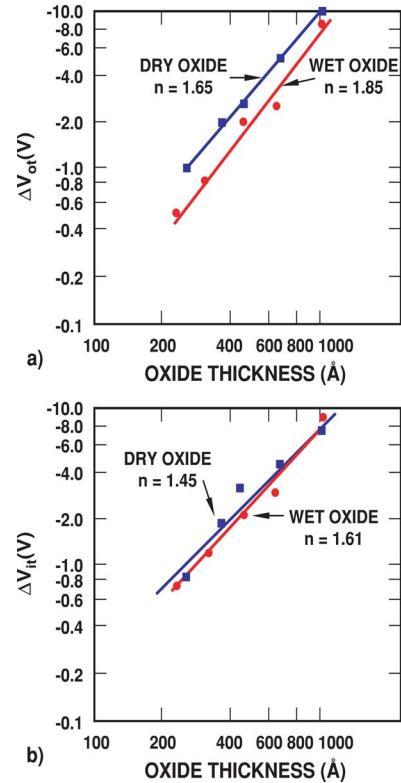

Fig. 8. The dependence of the threshold-voltage shift due to a) oxide-trap and b) interface-trap charge on oxide thickness.

key process condition that has a very large effect on gate-oxide hardness is oxide thickness. As the thickness of the gate oxide decreases, radiation hardness improves. Fig. 8 is a plot of the threshold-voltage shifts due to interface-trap and oxide-trapped charge for dry and steam grown (wet) oxides. The threshold-voltage shifts due to both types of charge decrease with slightly less than a  $t_{ox}^2$  thickness dependence ( $t_{ox}^{1.5}$  to  $t_{ox}^{1.8}$ ). For very thin oxides ( $< 20$  nm), there is evidence that the amount of radiation-induced oxide-trap charge decreases with an even faster dependence on oxide thickness [52]. Because of the improvement in hardness with decreasing thickness, gate oxides in advanced commercial technologies can be extremely radiation hard.

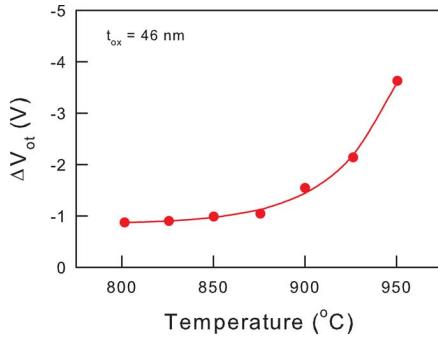

In addition to oxide thickness, other process conditions can affect hardness. For example, high-temperature anneals can significantly degrade device hardness due to the creation of oxygen vacancies in the oxide. Fig. 9 is a plot of  $\Delta V_{ot}$  for capacitors annealed in nitrogen at temperatures from 800 to 950°C and irradiated to 1 Mrad(SiO<sub>2</sub>) [53]. Anneal temperatures above 875°C lead to significant increases in  $\Delta V_{ot}$ . The trend in advanced commercial IC technologies is to minimize the time and temperature of anneals and oxidations to minimize the amount of dopant redistribution. Thus, minimizing anneal temperatures to improve radiation hardness is consistent with the present trend for manufacturing commercial ICs. Nitrogen anneals over the same temperature range have a much smaller effect on  $\Delta V_{it}$ .

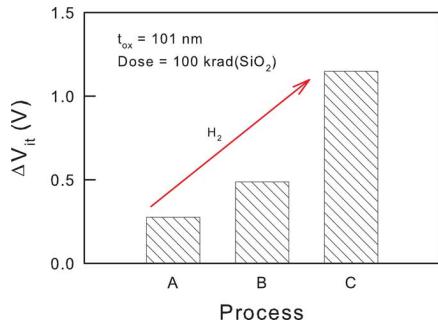

However, annealing in ambients containing hydrogen after depositing the gate material (e.g., polysilicon or metal) can significantly increase the amount of radiation-induced interface-trap charge. Fig. 10 is a plot of  $\Delta V_{it}$  for capacitors annealed

Fig. 9. The effect of anneal temperature on radiation-induced oxide-trapped charge. (After [53].)

Fig. 10. Effect of hydrogen on radiation-induced interface-trap buildup. Capacitor A was exposed to the least amount of hydrogen during processing and Capacitor C was exposed to the most amount of hydrogen. (After [54].)

in varying amounts of hydrogen after deposition of the polysilicon gate and irradiated to 100 krad( $\text{SiO}_2$ ) [54]. Capacitor A was exposed to the least amount of hydrogen and capacitor C was exposed to the greatest amount of hydrogen. Increasing the amount of hydrogen used in processing resulted in increasing concentrations of interface-trap charge. Thus, to optimize hardness, process temperatures after gate oxidation should be kept at or below 850°C (except perhaps for a few brief rapid thermal anneals) and ambients containing hydrogen should be minimized.

#### IV. ALTERNATE DIELECTRICS

Silicon dioxide has been the primary gate insulator since MOS ICs were first developed. To achieve the drive currents required by advances in IC technology, the thicknesses of  $\text{SiO}_2$  gates are becoming extremely thin. They are reaching a point where electron tunneling can cause prohibitively large increases in power consumption. To circumvent this problem, alternate gate dielectrics with high dielectric constants (also referred to as “high-k” dielectrics) are being explored. By using a high-dielectric-constant gate material, a much thicker dielectric can be used to obtain the equivalent capacitance of much thinner  $\text{SiO}_2$  gates. For these thicker high dielectric constant insulators, electron tunneling is reduced and oxide-trap charge may be more significant.

At the present time, there is relatively little information on the radiation hardness of the dielectrics under consideration for replacing  $\text{SiO}_2$ . Because the dielectric gates will be physically thicker and deposited or grown using different techniques, it is possible that these dielectrics could trap significantly more

Fig. 11. Midgap voltage shift versus total dose for hafnium silicate capacitors irradiated with 10-keV x-rays with applied biases from  $-1$  to  $2$  V. The equivalent oxide thickness (EOT) is 4.5 nm and the physical thickness is 29 nm. (After [55].)

charge than thinner thermally-grown  $\text{SiO}_2$  gates. As a result, the radiation-induced charge trapping in the gate insulator may once again affect IC radiation hardness. The radiation hardness of hafnium oxide,  $\text{HfO}_2$ , has been explored [55]–[59]. Hafnium oxide has a relatively high dielectric constant (25) compared to  $\text{SiO}_2$  (3.9), is less reactive with polysilicon than many of the other dielectrics being pursued, and has shown encouraging results in measurements of reliability such as stress-induced leakage current, time-dependent dielectric breakdown, and mean time to failure [60]–[63].

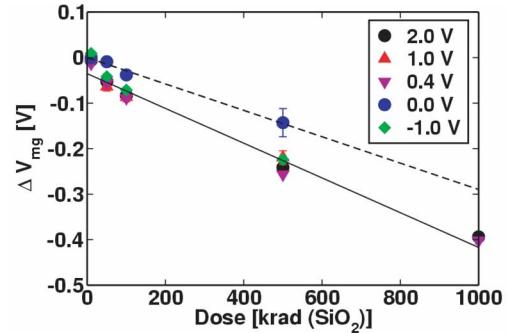

Fig. 11 is a plot of the midgap voltage shift for hafnium silicate capacitors irradiated with 10-keV x rays with an applied bias ( $-1$  to  $2$  V) during irradiation [55]. The physical oxide thickness of the hafnium silicate gates is 29 nm. This corresponds to an equivalent oxide thickness (EOT) of 4.5 nm. Assuming interface-trap charge is neutral at midgap, the midgap voltage shift is equal to the oxide-trap charge voltage shift. The midgap voltage shift is relatively large. After irradiating to 1 Mrad( $\text{SiO}_2$ ), the voltage shift is  $\sim -0.4$  V for capacitors irradiated with either a positive or negative bias and is approximately  $-0.3$  V for capacitors irradiated with a 0 V bias [55]. For a more practical hafnium oxide thickness ( $< 2$  nm EOT), as will be required by advanced technologies, the voltage shift may be considerably less.

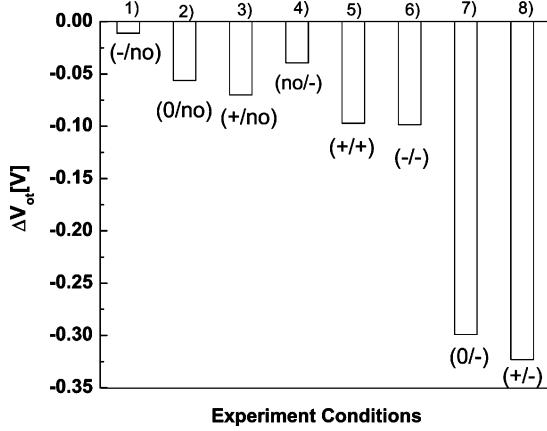

Although the radiation hardness of thin EOT  $\text{HfO}_2$  gate oxides appears to relatively good, recent results have shown that the combined effects of irradiation and bias temperature stress (BTS) can lead to enhanced degradation, as illustrated in Fig. 12 [59]. The amount of enhanced degradation was found to depend on the irradiation and anneal bias conditions. Worst-case bias was for pMOS transistors irradiated in their “OFF” states, and annealed in their “ON” states (the zero/minus state in Fig. 12).

Another alternative dielectric that has been explored in much more detail is reoxidized nitrided oxides (RNO) [64]–[69]. Nitrided oxides have a lower pin-hole density than  $\text{SiO}_2$ , can be grown at high temperatures permitting better uniformity and less compressive stress and fixed charge, and can retard the diffusion of dopants through the insulator which can affect the channel resistivity [65]. These properties make nitrided and RNO dielectrics attractive for ultra-thin gate-oxide commercial and hardened devices [65]. Indeed, most advanced commercial CMOS technologies in production today employ

Experiment Conditions

Fig. 12.  $\Delta V_{\theta t}$  at 1.0 Mrad( $\text{SiO}_2$ ) for  $\text{Al}/\text{HfO}_2 + \text{SiO}_x\text{N}_y/\text{Si}$  pMOS capacitors for: 1) negative-bias irradiation and no BTS; 2) zero bias irradiation and no BTS; 3) positive-bias irradiation and no BTS; 4) no irradiation and NBTS; 5) positive-bias irradiation and PBTS; 6) negative-bias irradiation and NBTS; 7) zero-bias irradiation and NBTS; and 8) positive-bias irradiation and NBTS. The bias stressing temperature is 75°C. Gate biases are  $\pm 0.3$  V or 0 V during irradiation, and  $\pm 0.3$  V during BTS. (After [59].)

nitrided oxides. RNO oxides have been shown to be superior to thermal oxides in radiation hardness [70]–[72] and hot-carrier degradation [73].

The primary difference between thermal and RNO dielectrics in ionizing radiation environments is the nearly total lack of interface-trap buildup for RNO dielectrics [72]. RNO dielectrics can be fabricated in which there is no measurable interface-trap buildup for transistors irradiated to total doses in excess of 50 Mrad(Si) [72]. For those cases where some interface-trap buildup was observed, the number of interface traps does not increase in time after irradiation [70]. This likely occurs because hydrogen released in the bulk of the dielectric or near the interface (which is responsible for interface-trap buildup in thermal oxides), cannot penetrate the nitrogen rich oxynitride layer near the interface and create an interface trap [70].

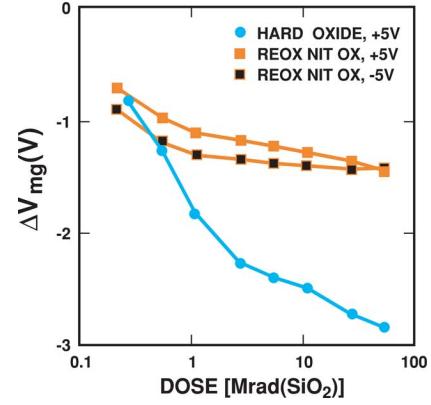

RNO dielectrics can be fabricated so that the amount of oxide-trap charge buildup for a RNO oxide is lower to or comparable to that for a thermal oxide. Fig. 13 [72] is a plot of the threshold-voltage shift at midgap for p-channel transistors fabricated with a hardened oxide and with a RNO oxide versus dose. The oxide and RNO dielectric thicknesses were 37 nm and the preirradiation fixed charge levels were  $\sim 3 \times 10^{10}$  and  $10^{11} \text{ cm}^{-2}$ , respectively. At midgap, interface-trap charge is neutral, thus the threshold-voltage shift at midgap corresponds to the threshold-voltage shift due to oxide-trap charge. The bias during irradiation for the hardened thermal oxide was +5 V and the bias for the RNO oxides was either +5 or -5 V. After irradiating to 10 Mrad( $\text{SiO}_2$ ), the amount of oxide-trap charge buildup in the hardened thermal oxides is more than twice that for the RNO oxides. Note that for the RNO oxide transistors, the shifts are nearly equal for biases of +5 and -5 V.

## V. PARASITIC FIELD OXIDE TRANSISTOR LEAKAGE

Even though the radiation hardness of commercial gate oxides may improve as the IC industry tends towards ultra-thin oxides, field oxides of advanced commercial technologies will

Fig. 13. The change in midgap voltage measured on 37 nm RNO and thermal oxide transistors versus dose. The midgap voltage shift corresponds to the threshold-voltage shift due to oxide-trapped charge. (After [72].)

still be relatively thick and may still be very soft to ionizing radiation. A relatively small dose in a field oxide (10 krad(Si) for some commercial devices) can induce sufficient charge trapping to cause field-oxide induced IC failure. Because of this, radiation-induced charge buildup in field oxides is the main cause of IC failure in advanced commercial technologies.

Field oxides are much thicker than gate oxides. Typical field-oxide thicknesses are in the range of 100 nm to 1000 nm. Unlike gate oxides, which are routinely grown by thermal oxidation, field oxides are produced using a wide variety of deposition techniques. Thus, the trapping properties of a field oxide may be poorly controlled and can be considerably different than for a gate oxide.

Even for thermally grown thick oxides, the buildup of charge in gate and field oxides can be qualitatively different [74], [75]. For example, in thick  $\text{SiO}_2$  capacitors ( $> 100$  nm), interface-trap buildup has been observed within 4 ms following a pulse of ionizing radiation [74]. The buildup was found to be independent of oxide field and polarity and occurred with approximately the same efficiency at room temperature and 77 K. This suggests that some “prompt” interface traps could have been created directly by radiation. This is in contrast to thinner gate oxides, where little or no prompt interface traps are normally observed. On similar devices, a significant amount of hole trapping was observed in the bulk of the oxide [75].

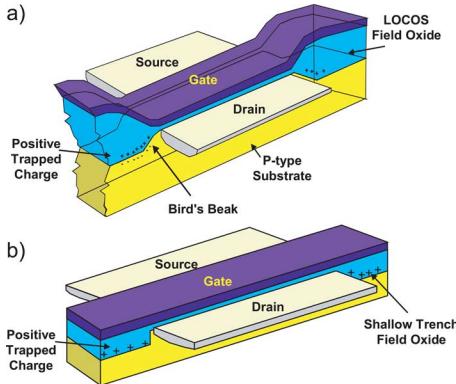

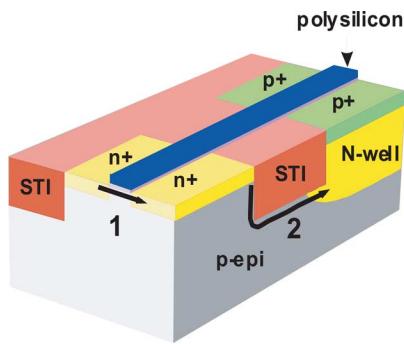

Two common types of field oxide isolation used today are local oxidation of silicon (LOCOS) and shallow-trench isolation (STI). LOCOS isolation has been used for many years. Within the last ten years, most commercial IC suppliers have replaced LOCOS isolation with STI for advanced submicron technologies. Fig. 14(a) [76] shows the cross-section of an n-channel transistor with LOCOS isolation, illustrating positive charge buildup in the bird’s beak regions. Similar charge buildup will occur for STI, as illustrated in Fig. 14(b) [76]. As positive radiation-induced charge builds up in the field oxide overlying a p-type surface, it can invert the surface, forming an n-type region underneath the field oxide. As the surface inverts, conducting paths can be generated that will greatly increase the leakage current. Fig. 15 depicts two possible leakage paths for STI [76]. One leakage path occurs at the edge of the gate-oxide transistor between the source and drain. Another leakage path

Fig. 14. Cross section of a) a LOCOS isolated and b) shallow-trench isolated transistor. (After [76].)

Fig. 15. As indicated by the arrows, two possible leakage paths in a shallow-trench isolation technology. (After [76].)

could occur between the n-type source and drain regions of a transistor and the n-well of adjacent p-channel transistors. These two leakage paths will cause an increase in static power supply current of an IC with radiation. Because radiation-induced charge buildup in field oxides is predominantly positive, its effect is usually most important for n-channel transistors.

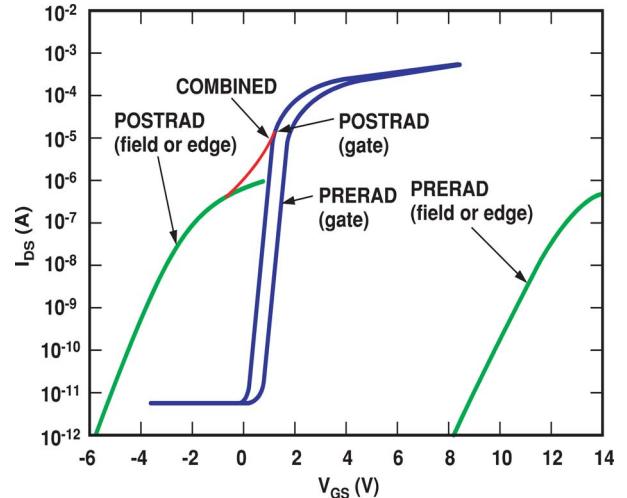

The field oxide forms a parasitic field-oxide transistor in parallel with the gate-oxide transistor. For example, at the edges of the gate transistor the gate polysilicon extends over the field oxide region, as shown in Fig. 14. The parasitic field-oxide transistor consists of the gate polysilicon, a portion of the field oxide, and the source and drain of the gate transistor. The effect of the excess leakage current from a parasitic field oxide transistor on the gate oxide transistor is illustrated in Fig. 16. Plotted in Fig. 16 are the drain-to-source leakage current versus gate-to-source voltage curves for an n-channel gate-oxide transistor with (combined curve) and without field-oxide leakage and for a parasitic field-oxide transistor. Because of the large thickness of the field oxide, the preirradiation threshold voltage of the parasitic field oxide transistor is relatively large, but as positive radiation-induced charge builds up in the field oxide, it can cause a very large negative threshold-voltage shift of the parasitic field-oxide transistor. If the threshold-voltage shift of the parasitic field oxide transistor is large enough (as depicted in Fig. 16), it will cause an "OFF" state leakage current ( $I_{DS} @ V_{GS} = 0$  V) to flow, which can significantly add to the drain-to-source current of the gate oxide transistor. Thus, the field-oxide leakage prevents the gate oxide transistor from

Fig. 16. I-V curves for a gate-oxide transistor and a parasitic field-oxide transistor showing the increase in leakage current of the gate-oxide transistor caused by the parasitic field-oxide transistor.

Fig. 17. Flatband voltage shift and the threshold-voltage shift due to oxide and interface-trap charge versus applied field during x-ray irradiation for an n-channel transistor fabricated using a traditional field oxide insulator as the gate dielectric. (After [76].)

being completely turned off. This will greatly add to the static supply leakage current of an IC.

The amount of field-oxide leakage depends greatly on IC process and topography. For example, for STI the topography of the shallow trench and process conditions inherently lead to variations in the trench sidewall insulator thickness between the silicon trench and overlying conductors (e.g., polysilicon). This is especially pronounced at the top corner of the trench. At the top corner, the shallow insulator thickness can result in very high fields across the insulator. These high fields in trench corner regions have been shown to reduce gate oxide integrity [77], to cause anomalous humps in the subthreshold I-V characteristics of non-irradiated commercial ICs [77]–[82], and to severely limit the irradiation hardness [76]. As the magnitude of the electric field across the trench corner increases, the magnitude of the threshold-voltage shift of the parasitic field-oxide transistor increases [76].

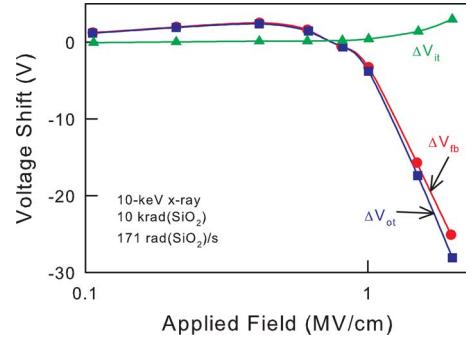

The worst-case bias condition for radiation-induced charge buildup in field oxides is the bias condition that maximizes the electric field across the field oxide. This is clearly shown in Fig. 17, which is a plot of the total threshold-voltage shift (plotted as  $\Delta V_{FB}$ ) and the threshold-voltage shift due to

oxide and interface-trap charge versus applied electric field for transistors fabricated using a field oxide as the gate dielectric [76]. The gate dielectric was deposited using a traditional shallow-trench isolation process. The transistors were irradiated with 10-keV x rays to a total dose of 10 krad( $\text{SiO}_2$ ). For these bias and irradiation conditions, there is no significant buildup of interface-trap charge in the field oxide. However, at the higher electric fields, there is a very large radiation-induced buildup of oxide-trapped charge, which causes a very large threshold-voltage shift of the field oxide transistor. After irradiating to a total dose of 10 krad( $\text{SiO}_2$ ), the threshold-voltage shift was greater than 25 V for electric fields greater than 2 MV/cm. Depending on the initial threshold voltage of the field oxide transistor, this radiation-induced threshold-voltage shift may be large enough to cause large increases in transistor leakage current. These data demonstrate that one must reduce the electric field in the field oxide to avoid large increases in radiation-induced field oxide leakage current. Even though traditional process techniques were used to deposit the gate dielectric, the topology of the gate dielectric for these transistors is considerably different than for standard STI. Very high electric fields can occur at the corners of STI, leading to very large radiation-induced threshold-voltage shifts of parasitic STI transistors. In a typical layout of STI, a polysilicon line connected to the gate of a transistor can extend over the STI. Thus, the bias condition that will result in the maximum electric field across the STI is the bias condition that gives the maximum voltage drop between the gate and the substrate. This bias condition is normally the “ON” bias condition, where the gate is at the bias supply voltage,  $V_{DD}$ , and the source, drain, and substrate are grounded. Although these results were demonstrated for STI, similar results have been obtained for ICs with LOCOS isolation.

## VI. SOI TECHNOLOGIES

### A. General

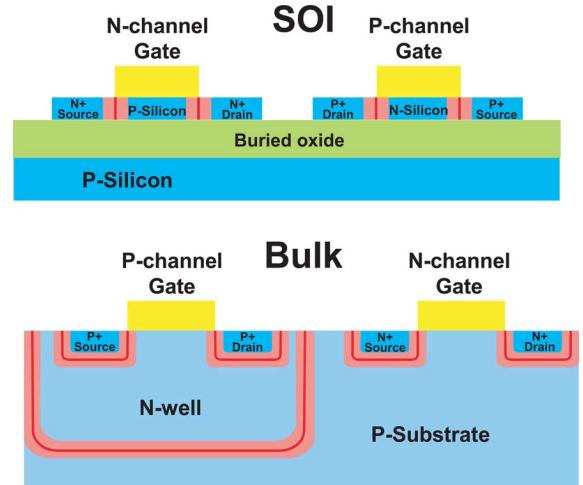

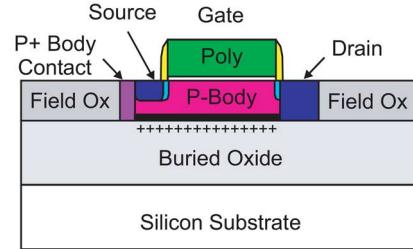

Silicon-on-insulator (SOI) technology has been actively pursued for use in radiation-hardened systems for more than twenty years. More recently, it is quickly becoming a mainstream technology for commercial applications. The cross sections of SOI (top) and bulk-silicon (bottom) n- and p-channel transistors are shown in Fig. 18. The main feature that has made SOI technology attractive for radiation-hardened and commercial applications is that SOI transistors are built on top of an oxide instead of a silicon substrate. In a standard thin-film SOI transistor, the source and drain extend completely through the top-silicon layer, which is typically less than 200 nm thick. Except for the fact that SOI transistors are built on an oxide, SOI process technology is very similar to that for bulk-silicon technologies. Each SOI transistor inherently includes two transistors: a standard top-gate transistor consisting of the source, drain, and gate oxide, and a back-gate parasitic transistor consisting of the source and drain of the top-gate transistor and the buried oxide. For the back-gate transistor, the substrate acts as the gate contact. Two generic types of SOI transistors (top gate) are partially-depleted and fully-depleted transistors. In a partially-depleted transistor, the depletion region in the

Fig. 18. Cross sections of SOI (top) and bulk-silicon (bottom) n- and p-channel transistors.

body region (the region underneath the gate) formed by the top-gate transistor does not extend completely through the top-silicon layer. Because there is a non-depleted silicon region between the top-gate depletion region and the silicon/buried oxide interface, the top-gate transistor characteristics of a partially-depleted transistor (i.e., threshold voltage) are not directly affected by charge buildup in the buried oxide. In a fully-depleted transistor, the depletion region formed by the top-gate transistor extends completely through the top-silicon layer. For a fully-depleted transistor, the top gate transistor is electrically coupled to the back-gate transistor and radiation-induced charge buildup in the buried oxide will directly affect the top-gate transistor characteristics. Whether a transistor is a partially or fully-depleted transistor depends primarily on the thickness of the silicon layer and the doping concentration of the body region. A fully-depleted transistor must have a very thin silicon layer and/or be lightly doped.

### B. Total-Dose Effects

The total-dose hardness of an SOI transistor depends on the radiation hardness of three oxides: 1) gate, 2) field oxide or side-wall isolation, and 3) buried oxide. The mechanisms for the radiation-induced degradation of the gate oxide of a MOS/SOI transistor are identical to the mechanisms for the gate oxide of a MOS transistor fabricated on a bulk silicon substrate as discussed above. Most present-day SOI circuits use shallow-trench isolation for transistor isolation. The radiation hardness of STI was discussed above.

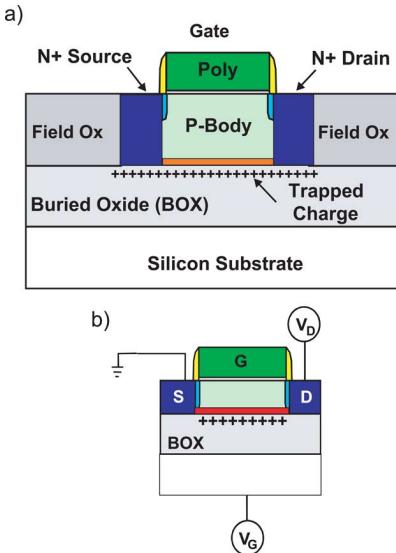

1) *Partially-Depleted Devices*: The biggest difference between the total-dose response of SOI and bulk-silicon technologies is radiation-induced charge buildup in the buried oxide of SOI transistors. As SOI buried oxides are exposed to ionizing radiation, radiation-induced charge will become trapped in the buried oxide. This radiation-induced trapped charge is predominantly positively charged. As illustrated in Fig. 19(a), this charge buildup in the buried oxide can invert the back-channel interface, forming a leakage path between the source and drain of the top-gate transistor. For simplicity, the charge buildup as illustrated in Fig. 19(a) is shown to be located close

Fig. 19. Cross section of an SOI transistor illustrating a) charge buildup in the buried oxide inverting the back-channel and b) bias conditions for measuring the back-channel threshold voltage.

to the buried oxide/back-channel interface. However, in general, charge will be trapped throughout the buried oxide. Inversion of the back-channel interface can lead to large increases in the leakage current of a partially-depleted transistor. Because the top-gate transistor is electrically coupled to the back-gate transistor in a fully-depleted transistor, radiation-induced charge buildup in the buried oxide of a fully-depleted transistor will cause a decrease in the threshold voltage of the top-gate transistor. In the remainder of this section, we examine the effects of radiation-induced charge buildup in the buried oxide on transistor radiation hardness.

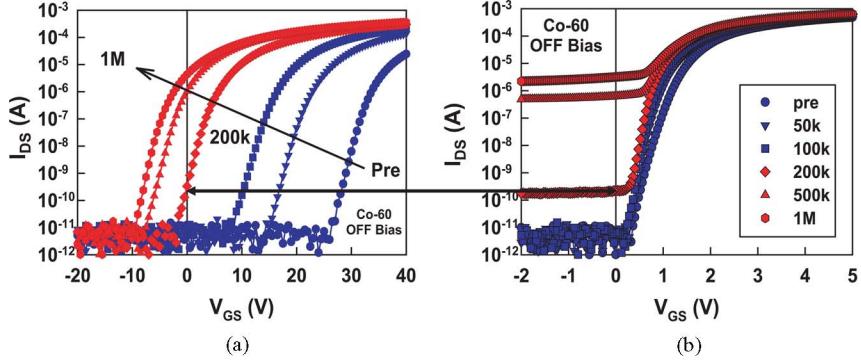

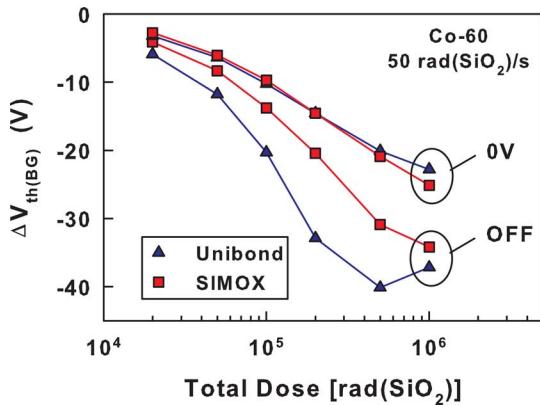

A simple method for quantifying the amount of radiation-induced charge buildup in the buried oxide is to measure the threshold voltage of the back-gate transistor. The bias configuration for measuring the back-gate I-V characteristics is shown in Fig. 19(b). The bias configuration and measurement conditions are identical to those for measuring the top-gate I-V characteristics, except that the gate bias is applied to the substrate. Typical I-V curves for the back-gate transistor are shown in Fig. 20(a). The transistors were irradiated with Co-60 gamma rays in the OFF ( $V_{GS} = V_S = 0$  V;  $V_{DS} = 5$  V) bias condition. As noted in the figure, positive charge buildup in the buried oxide can cause large negative shifts in the back-gate transistor I-V curves. As the radiation-induced charge buildup becomes sufficiently large to cause an increase in the leakage current at zero back-gate bias, the top-gate leakage current will begin to increase as illustrated in Fig. 20(b). This leakage current resulting from radiation-induced charge buildup in the buried oxide will prevent the top-gate transistor from being completely turned off. If it is large enough, it can cause parametric and potentially functional failure.

The radiation response of buried oxides has been found to be highly dependent on the fabrication process [83], [84]. Two common methods for fabricating SOI substrates are separation by implanted oxygen (SIMOX) and by wafer bonding. SIMOX substrates are formed by implanting a silicon substrate with

oxygen ions to very high fluence levels and then annealing the substrate at very high temperatures (e.g., 1350°C) to form the buried oxide. Bonded SOI substrates are formed by growing an oxide on the surface of one wafer and then bonding the wafer to a second substrate. There are numerous methods for producing the thin top silicon layer of the SOI substrate. Common to all bonded wafer processes is a high temperature bond strengthening anneal (e.g., 1100°C). The high temperature anneals used to fabricate SOI substrates (both SIMOX and bonded) cause oxygen to out-diffuse from the buried oxide, leaving behind numerous oxide defects. These defects can lead to radiation-induced trapped charge. It is natural to expect that the high-fluence implants used to fabricate SIMOX substrates (and some bonded oxide substrates) may cause numerous implant-related defects throughout the buried oxide. Previous works [84]–[88] have shown that up to 100% of the radiation-generated holes are trapped in the bulk of the oxide at deep trap sites close to their point of origin. An example of the threshold-voltage shifts for two SIMOX and bonded wafers is shown in Fig. 21 [89]. Data are shown for the back-gate threshold-voltage shift for transistors fabricated using SIMOX and Unibond (made by SOITEC) substrates, irradiated using Co-60 gamma rays in the 0 V ( $V_{GS} = V_S = V_{DS} = 0$  V) and OFF ( $V_{GS} = V_S = 0$  V;  $V_{DS} = 5$  V) bias conditions. In this comparison, the Unibond substrates show larger back-gate transistor threshold-voltage shifts for the OFF bias condition than the SIMOX substrates. However, more recent Unibond substrates with thinner buried oxide thicknesses exhibit far less threshold-voltage shifts. Once trapped, some of the holes are slowly neutralized by electrons by thermal detrapping at room temperature [84]–[88]. In addition to hole trapping, electrons are also trapped throughout the bulk of the buried oxide [84]. Most of the trapped electrons are thermally detrapped within  $< 1$  s after a pulse of radiation. After the electrons are detrapped, the resultant charge is due to a high concentration of trapped holes causing large negative threshold-voltage shifts of the buried oxide.

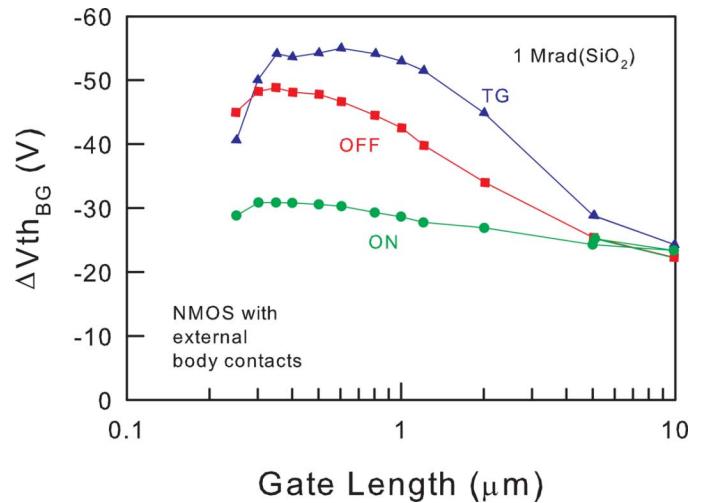

Liu *et al.* [90] was the first to examine in detail the electric field conditions in a partially-depleted SOI buried oxide that lead to worst-case bias conditions. Similar to field oxides, the buildup of radiation-induced charge in SOI buried oxides is dominated by positive oxide-trapped charge. Therefore, the electric field condition that results in the maximum back-gate threshold-voltage shift in an SOI transistor is the bias condition that causes the most radiation-induced hole trapping near the back Si/SiO<sub>2</sub> interface. This will be the bias condition that results in the maximum electric field strength in the buried oxide underneath the channel region. Liu *et al.* [90], and subsequently Ferlet-Cavrois *et al.* [91], have simulated the electric field distributions in the buried oxide for numerous radiation bias conditions. Both showed that for typical gate lengths and buried oxide thicknesses the bias condition that produces the largest electric fields underneath the channel and the most hole trapping is the transmission gate (pass gate) bias configuration for partially-depleted transistors. The transmission gate (TG) bias configuration is defined as source and drain biased at  $V_{DD}$  and gate and body contact (if available) grounded. Simulations and data [91] have also shown that the OFF bias condition (drain at

Fig. 20. I-V characteristics for a) a back-gate transistor irradiated to 1 Mrad( $\text{SiO}_2$ ) and its effect on b) the top-gate transistor leakage current. The transistors were irradiated in the OFF ( $V_{GS} = V_S = 0$  V;  $V_{DS} = 5$  V) bias condition.

Fig. 21. Back-gate transistor threshold-voltage shift for SOI transistors fabricated using Unibond and SIMOX buried oxides. (After [89].)

$V_{DD}$  and all other contacts grounded) can result in very large back-gate threshold-voltage shifts. The bias configuration that results in the largest back-gate threshold-voltage shifts depends on the ratio of the transistor gate length to the buried oxide thickness [91]. These simulations have been experimentally verified [89]–[91]. Fig. 22 is a plot of the measured back-gate threshold-voltage shifts versus gate length for n-channel transistors irradiated with 10 keV x rays to a total dose of 1 Mrad( $\text{SiO}_2$ ) [80]. The buried oxide thickness was 413 nm. The technology used for fabricating the transistors was a 0.25- $\mu\text{m}$  technology. The largest back-gate threshold-voltage shifts observed were in transistors irradiated in the TG bias configuration. However, for transistors with gate lengths near the standard technology gate length of 0.25  $\mu\text{m}$ , the back-gate threshold-voltage shifts were approximately the same for transistors irradiated in the TG and OFF bias configurations. The smallest back-gate threshold-voltage shifts were for transistors irradiated in the ON bias configuration. These results for the worst-case bias configuration for partially-depleted SOI transistors are just the opposite of that for the worst-case bias configuration for radiation-induced charge buildup in field oxides.

2) *Advanced Fully-Depleted Devices*: Compared to partially-depleted transistor circuits, fully-depleted SOI devices have been shown to be much more sensitive to radiation-induced oxide charge buildup in the buried oxide and interface-trap

Fig. 22. Back-gate threshold-voltage shift versus gate length for an n-channel SOI transistor irradiated with x rays to a total dose of 1 Mrad( $\text{SiO}_2$ ). Transistors were biased in the ON, OFF, and TG bias configurations. (After [91].)

buildup at the top buried oxide/silicon interface. Because the top-gate is electrically coupled to the back-gate, charge trapping in the buried oxide directly affects top-gate transistor characteristics. Charge trapping in the buried oxide decreases the top-gate threshold voltage of an n-channel transistor. This negative threshold voltage shift has also been shown to depend on the geometry (gate length and/or width) and the architecture (with or without body ties) of the device.

In advanced fully-depleted SOI devices, with gate lengths in the range of several tens of nanometers, total ionizing dose effects have been shown to be highly dependent on device architecture. A radiation-induced high current regime can exist in floating body devices, both at high and low drain voltages. This high current regime is attributed to a floating body effect, and is sometimes referred to as a “total dose latch” or snap-back effect [92]–[94]. Using a doped Si film in the body is an effective method for mitigating this sensitivity to high leakage current. The use of external body contacts in the device also prevents the onset of this leakage current. Devices with external body contacts are not sensitive to this high current regime, whatever their geometry. In addition, they are shown to be able to withstand an amount of total dose irradiation typical of most space

applications, and still be within margins for a low power technology [95], [96].

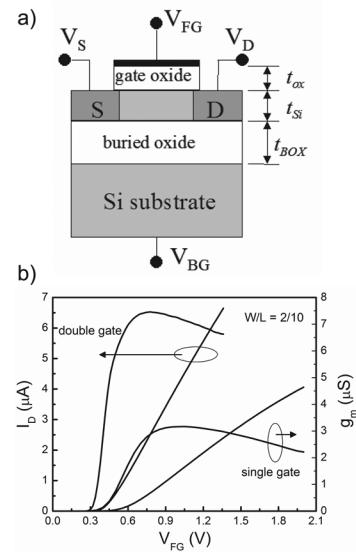

3) *Advanced Multiple-Gate Devices*: As CMOS technology continues to develop and scale, the trend has been to reduce dimensions to achieve better performance. The quest started with bulk CMOS devices. SOI devices were developed to accelerate Moore's law even further. Single-gate SOI devices were scaled first as partially-depleted and then as fully-depleted structures. As scaling continues, parasitic effects known as "short-channel effects" arise and limit the interest of these technologies. The need to suppress these short channel effects and to enhance carrier transport and mobility requires significant innovation. Multi-gate structures have long been foreseen as excellent candidates to that purpose, but technological difficulties have been difficult to overcome. Recently, the development of 3D multi-gate transistor structures has reached a new level, and advanced triple-gate MOSFETs exhibit very promising performances [96].

Radiation-induced degradation in these 3D structures is expected to be significantly reduced, because of the excellent gate control over the channel. However, there are still very few experimental studies of charge trapping properties in these devices [97]–[101]. As expected, the efficient control provided by the lateral gates over the electrostatic potential throughout the Si film screens the influence of the charge trapped in the gate and buried oxides. The impact on the electrical characteristics of the FinFET is negligible, and these 3D devices can withstand large amounts of total dose. In addition, due to the shape of the surrounding gate, charge trapping is reduced under the channel region. The penetration of lateral gates into the buried oxide forces the radiation-generated holes towards the lateral gates in the bulk of the buried oxide, where their trapping has less of an impact on the device electrical response. The  $\Omega$ -gate FET architecture has been shown to be the most tolerant multi-gate structure to total dose irradiation [96], [99].

### C. Hardening

Several techniques have been proposed to mitigate the effects of radiation-induced charge trapping in the buried oxide on transistor performance. These techniques can be grouped into two general categories: techniques that reduce the amount of net positive radiation-induced trapped charge and techniques that reduce the effects of radiation-induced trapped charge on transistor performance. One technique that has been proposed to reduce the amount of net radiation-induced positive trapped charge is to implant the buried oxide with silicon [102], [103]. The silicon implant creates electron traps throughout the buried oxide. When filled, these electron traps will compensate the trapped positive charge, decreasing the net positive charge in the oxide.

A transistor structure that reduces the effect of radiation-induced charge trapped in the buried oxide on transistor performance is the body-under-source field effect transistor (BUSFET) [104]. The BUSFET is similar to a standard SOI transistor, except that the source penetrates only partially through the top silicon layer. (If the drain also penetrates only partially through the top-silicon layer, there could be a large

Fig. 23. Cross section of a BUSFET transistor illustrating the shallow source. For a BUSFET transistor, inversion of the back-channel interface by charge trapping in the buried oxide does not form a conducting path between source and drain. (After [104].)

Fig. 24. a): schematic cross-sectional diagram of a fully depleted SOI MOSFET. b): current-voltage and transconductance characteristics for fully depleted nMOS transistors operated in double gate mode. (After [100].)

decrease in dose rate and single-event upset hardness due to additional junction area.) The cross section of a BUSFET is shown in Fig. 23. Inherent to the BUSFET is a body tie that connects the body region to a p+ body contact at all positions along the width of the channel. This makes the BUSFET body tie more effective than conventional body ties. As radiation-induced charge is trapped in the buried oxide, the charge will invert the back-channel interface. However, because the source penetrates only partially through the buried oxide, the inverted layer cannot form a conducting path between the source and drain and no increase in top-gate transistor leakage current occurs. As long as the depletion region formed by the electron layer does not come into contact with the source depletion region, there will be no conducting path between source and drain.

For SOI technologies with hardened buried oxides, opportunities to operate the devices in double gate mode, as illustrated in Fig. 24 [100], and other novel device structures also make SOI of continuing interest for future radiation-tolerant microelectronics. Fig. 24 illustrates that front to back-gate coupling of the electric fields can lead to improved device mobility and potentially enhanced radiation response in double gate mode of device operation.

Fig. 25. Oxide trap charge densities for Al-gate MOS capacitors irradiated with 10-keV X-rays at an applied electric field of  $\sim 1.5$  MV/cm and dose rate of  $\sim 1$  krad( $\text{SiO}_2$ )/min. (After [109].)

## VII. EFFECTS OF AGING

Exposure of devices to hydrogen post processing has been shown to lead to increased interface-trap buildup [105]–[108]. In 1988, it was shown that hydrogen (0.3 to 0.6%  $\text{H}_2$ ) trapped in hermetically sealed ceramic packages can increase radiation-induced charge buildup in MOS devices [105]. More recently, it was shown that hydrogen trapped in hermetically sealed packages can also degrade the total dose response of bipolar linear devices [106]–[108]. These works suggest that hydrogen can readily diffuse into device oxides affecting radiation-induced charge buildup. Because hydrogen diffusion is a thermally activated process (time dependent), they also suggest that long-term exposure to hydrogen present in device packages may also lead to enhanced radiation-induced charge buildup. The military standard test method for internal gas analysis, Mil-Std-883, Method 1018 checks the amount of moisture in hermetically sealed packages, but it does not require a test for hydrogen or other gas impurities. As a result, many hermetic packages may contain significant amounts of hydrogen, 2 to 4% [106]. This raises the concern that long-term aging could lead to increased radiation-induced degradation.

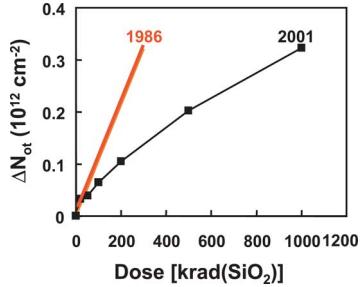

Indeed, significant changes in MOS oxide-trap charge and interface-trap charge have been observed with differences in aging times and/or thermal histories before irradiation. For example, Fig. 25 shows a comparison of oxide-trap charge density for MOS capacitors with 33.4 nm oxides irradiated in 1986, compared to devices from the same wafer irradiated 15 years later [109]. In this case, less oxide-trap charge is observed. However, a subsequent heat treatment of these capacitors (processed with no passivation layers, and given a high-temperature anneal to increase their O vacancy density [110] before irradiation restores the original radiation response. In this case it is assumed that the absorption of moisture passivated some hole trapping sites, but baking the device removed the passivating species, likely a hydrogen complex [109].

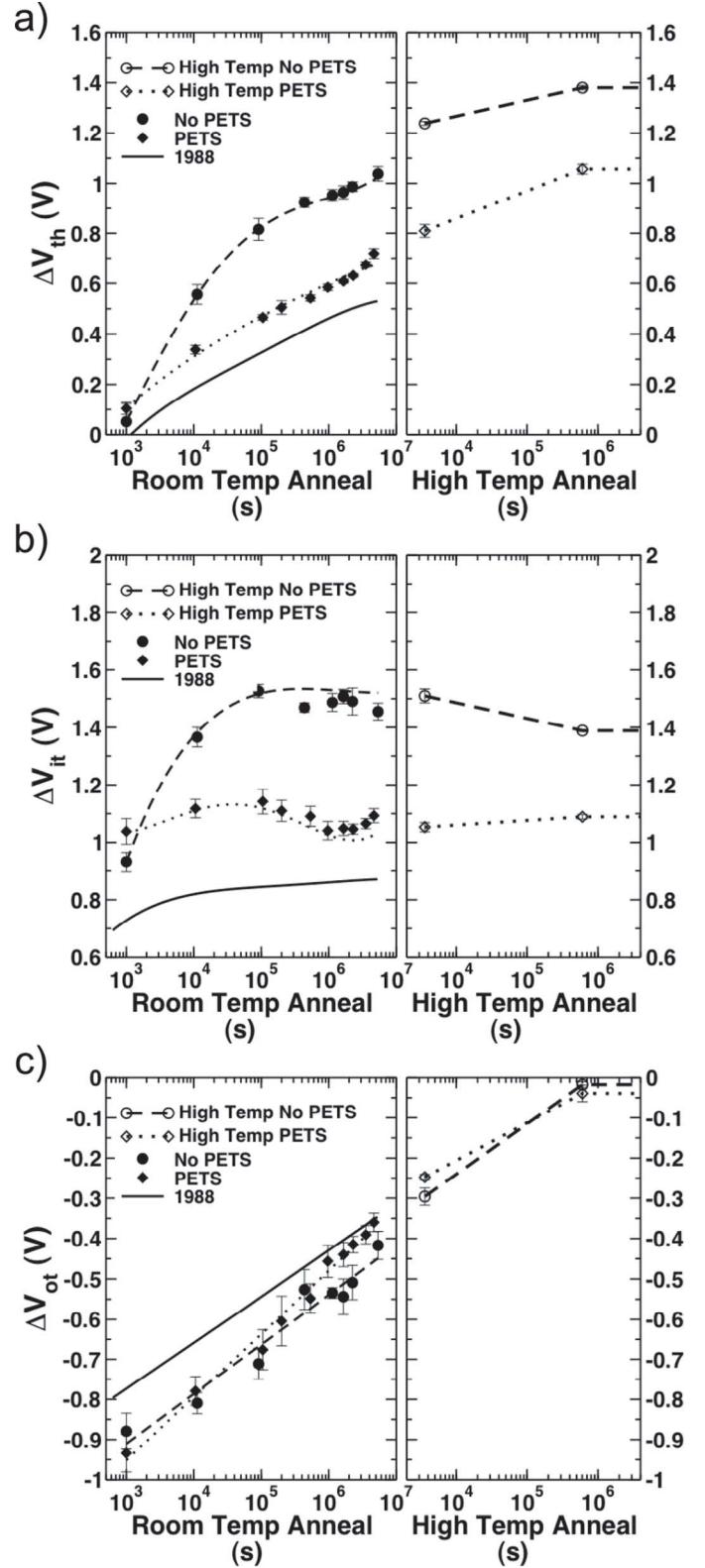

Aging has also been shown to degrade MOS radiation response. Fig. 26 shows experiments that were performed on fully processed MOS devices with P-glass (3% P-doped  $\text{SiO}_2$ ) passivation layers [16]. Devices tested for aging effects in [16] include nMOS transistors processed at Sandia National Laboratories in 1984, with poly-crystalline Si gates and oxide thicknesses of 32 nm or 60 nm. All irradiations were performed with a 10-keV X-ray irradiator at room temperature at 6 V bias. Some devices were baked before irradiation. Devices were annealed at

Fig. 26.  $\Delta V_{\text{th}}$  (a),  $\Delta V_{\text{it}}$  (b), and  $\Delta V_{\text{ot}}$  (c) for 60 nm gate oxide nMOS transistors stored hermetically since 1987 vs. postirradiation anneal time for exposures to 100 krad( $\text{SiO}_2$ ). The irradiation and anneal bias was 6 V. The 1988 data are from [16]. (After [111].)

room temperature and then at 100°C at 6 V bias. Fig. 26(a) compares threshold voltage shifts for nMOS transistors for 32 nm

Fig. 27. Input bias current as a function of dose and pre-irradiation elevated temperature stress (PETS) time for LM111 devices from National Semiconductor irradiated at 0 V at a dose rate of 0.1 rad(SiO<sub>2</sub>)/s. Increasing the duration of the PETS treatment reduces the enhancement of damage at low dose rate in these devices. (After [115].)

oxide parts irradiated in 1988 [16] and in 2005 [111]; the latter exposures were performed with and without exposure to pre-irradiation elevated temperature stress (PETS). The threshold-voltage rebound for parts irradiated in 2005 is much larger than for parts irradiated in 1988 (Fig. 26(a)). Fig. 26(b) shows the estimated threshold-voltage shifts due to interface-trap charge  $\Delta V_{it}$  for the 32 nm parts. By the end of the post-irradiation room-temperature anneal, the values of  $\Delta V_{it}$  for parts not exposed to PETS are  $\sim 67\%$  greater than the maximum  $\Delta V_{it}$  experienced by these parts in 1988. However, when parts are exposed to PETS prior to irradiation, these shifts in magnitude decrease substantially, but are still greater than the 1988 values [16], [111], [112]. Fig. 26(c) shows the shifts in threshold voltage due to oxide-trap charge  $\Delta V_{ot}$  for the 32 nm gate oxide transistors [111]. Much less change during irradiation and annealing is observed for  $\Delta V_{ot}$  with aging or baking than for  $\Delta V_{it}$ . These changes in  $\Delta V_{it}$  have been attributed to moisture absorption and the subsequent transport and reactions of water in the sensitive gate oxide region [111], [113].

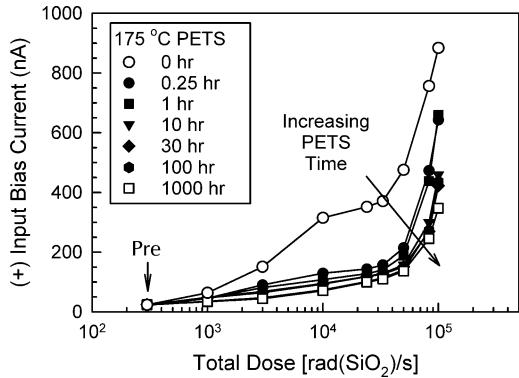

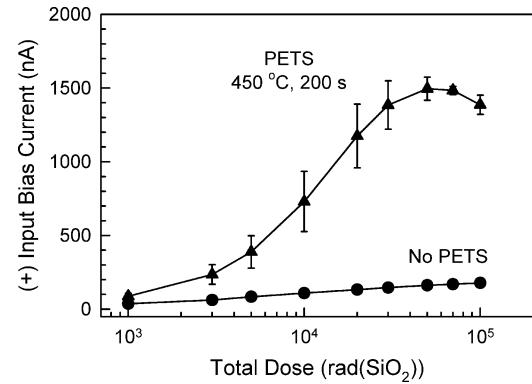

Bipolar linear microcircuits also are sensitive to PETS, as shown previously by Pease *et al.* for LT1014 and LM111 devices [114]. It was suggested that a reduction in interface-trap density and an increase in oxide-trap charge density were responsible for the effects observed in these devices. An extreme sensitivity to PETS effects was observed by Shaneyfelt *et al.* in linear bipolar ICs that also exhibited enhanced low-dose-rate sensitivity (ELDRS) associated with enhanced interface-trap formation during low-dose-rate irradiation, relative to higher-rate irradiation [115]. Remarkably, baking devices at modest temperatures (100 to 200°C) was found to almost entirely remove ELDRS for LM111 devices manufactured by National Semiconductor (Fig. 27). It was suggested that the interrelation between PETS and ELDRS might be attributable to a mutual dependency of the two phenomena on hydrogen in the thick, low-quality oxides that passivate base-emitter junctions [115]. Baking devices at 450°C for 200 s was found, in remarkable contrast, to increase the radiation sensitivity of the same LM111 devices (Fig. 28) at higher dose rates. These results suggest a complex interaction can occur between hydrogen species and precursor defects to radiation damage. These defects include oxygen vacancies in

Fig. 28. Input bias current as a function of dose and pre-irradiation stress for LM111 devices from National Semiconductor irradiated at 0 V at a dose rate of 50 rad(SiO<sub>2</sub>)/s. (After [115].)

SiO<sub>2</sub> that are trapped-hole precursors and dangling bonds at the Si/SiO<sub>2</sub> interface, which typically are passivated by hydrogen prior to radiation exposure or high-field stress, that are interface-trap precursors [116]. This illustrates the so-called “dual role” for hydrogen – it is beneficial to device response when it acts to passivate defects, but it can degrade device response when it reacts to create new defects [117]. This complicates the analysis and prediction of aging effects in MOS and bipolar devices [112].

Another complication in analyzing and predicting aging effects is the impact of passivation layers on ELDRS (PETS). Previous works have shown that some types of passivation layers can significantly reduce or eliminate ELDRS (PETS) [118]–[120]. How passivation layers affect the mechanisms of hydrogen interactions in oxides (and/or stress [115]) on ELDRS is not fully understood. Clearly, more work needs to be performed in this area to better analyze and predict aging effects in MOS and bipolar devices.

## VIII. HEAVY-ION EFFECTS

### A. Oxide Breakdown

A single-event gate rupture (SEGR) can occur as a single heavy ion passes through a gate oxide. SEGR occurs at high oxide electric fields, such as those during a write or clear operation in a nonvolatile SRAM or E<sup>2</sup>PROM [121]–[123]. SEGR was first observed [122], [123] for metal nitride oxide semiconductor (MNOS) dielectrics used for memory applications. Since then, SEGR has been observed in power MOSFETs, MOS transistors [124], and more recently in high-density DRAMs [125] and field-programmable gate arrays [126].

SEGR is caused by the combination of the applied electric field and the energy deposited by the ion [125], [127]. As an ion passes through a gate oxide it forms a highly conducting plasma path (conducting pipe) between the silicon substrate and the gate contact [121], [123], [124]. With an electric field across the oxide, charge will flow along the plasma path depositing energy in the oxide. The average resistance of the conducting pipe depends on the mobility of carriers and their density in the pipe. There are two sources of charge carriers in the conducting pipe: charge injected from the anode due to the electric applied across the oxide and charge generated in the oxide by the passage of

a heavy ion [127]. If the energy deposited is high enough, it can cause localized heating of the dielectric and potentially a thermal runaway condition. If thermal runaway occurs, the local temperatures along the plasma will be high enough to cause thermal diffusion of the gate material, cause the dielectric to melt, and evaporate overlying conductive materials [121], [124]. The resistance of the initial ion track is inversely proportional to the ion LET. If the LET is increased, the resistance is lowered, and the required voltage across the device to sustain conduction is reduced [124].

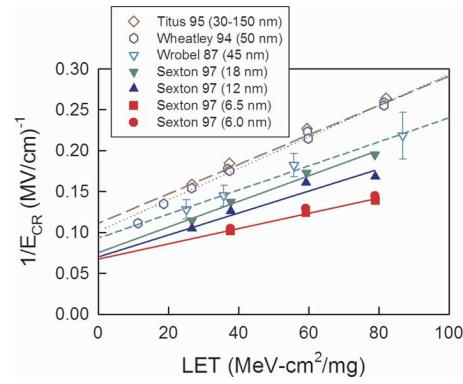

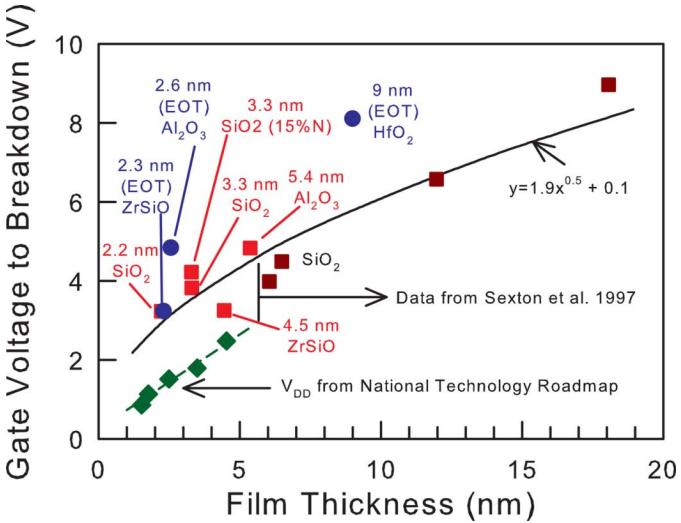

For thermal  $\text{SiO}_2$  oxides with the incident ion normal to the surface, Wheatley *et al.* [128] showed that the critical electric field,  $E_{cr}$ , for SEGR is given by

$$E_{CR} = \frac{E_0}{\frac{1+L}{B}} \quad (4)$$

where  $E_0$  is the breakdown field of the oxide in the absence of ion exposure in MV/cm,  $L$  is the ion LET in  $\text{MeV}\cdot\text{cm}^2/\text{mg}$ , and  $B$  is a fitting parameter. Sexton *et al.* [127] has derived an expression for  $B$ ,

$$B = \frac{\mu_1 n(V)}{\mu_2 K} \quad (5)$$

where  $\mu_1$  and  $\mu_2$  are the mobilities of carriers generated by high field injection and by the heavy ion, respectively,  $n(V)$  is the electron density from high field injection, and  $K$  is a proportionality constant determined assuming that the density of carriers is proportional to LET. For oxides with thicknesses from 6 to 18 nm, Sexton *et al.* [129] found that  $B$  varies from 48 to 72. As illustrated in Fig. 29, (4) does fit experimental data. This figure is a plot of  $1/E_{CR}$  versus LET for data taken from several different works [124], [128]–[130]. All of the data were taken on capacitors. In this figure,  $1/E_0$  is the y-axis intercept of the line and the slope of the line is equal to  $1/(E_0 B)$ . The data show a pattern of increasing breakdown field with decreasing oxide thickness, even at high LET [129], suggesting for a given LET that advanced technologies should become less susceptible to SEGR as gate oxide thickness decreases. Sexton *et al.* [129] have shown that  $E_0$  determined from the y-axis intercept is close to the experimentally measured pre-irradiation breakdown field (at least for the oxides explored in [129]). This is an indication that the improvement in SEGR for decreasing oxide thickness is fundamentally a function of the quality of the oxides prior to exposure to heavy ions.